With the importance of an ever-increasingly connected world beyond 5G, this gives rise to unprecedented, abundant data that poses a challenge to edge computing. As the scaling of transistors reaches its physical limits, the challenges in achieving computation power improvement becomes more significant. Hence, the integration of logics, memories, and sensors using emerging electronic materials in a memory-centric computing architecture is touted to be a viable solution to the von Neumann bottleneck.

In this computing paradigm shift, one of the fundamental challenges lies in the need for a reliable approach to achieve high performance devices for data processing, while allowing for low-temperature integration of these devices for M3D stacked layers at the CMOS Backend of line layers. However, the progress in pushing such technology towards commercialization has been slow due to the absence of a reliable semiconductor material with performance that can rival that of conventional silicon.

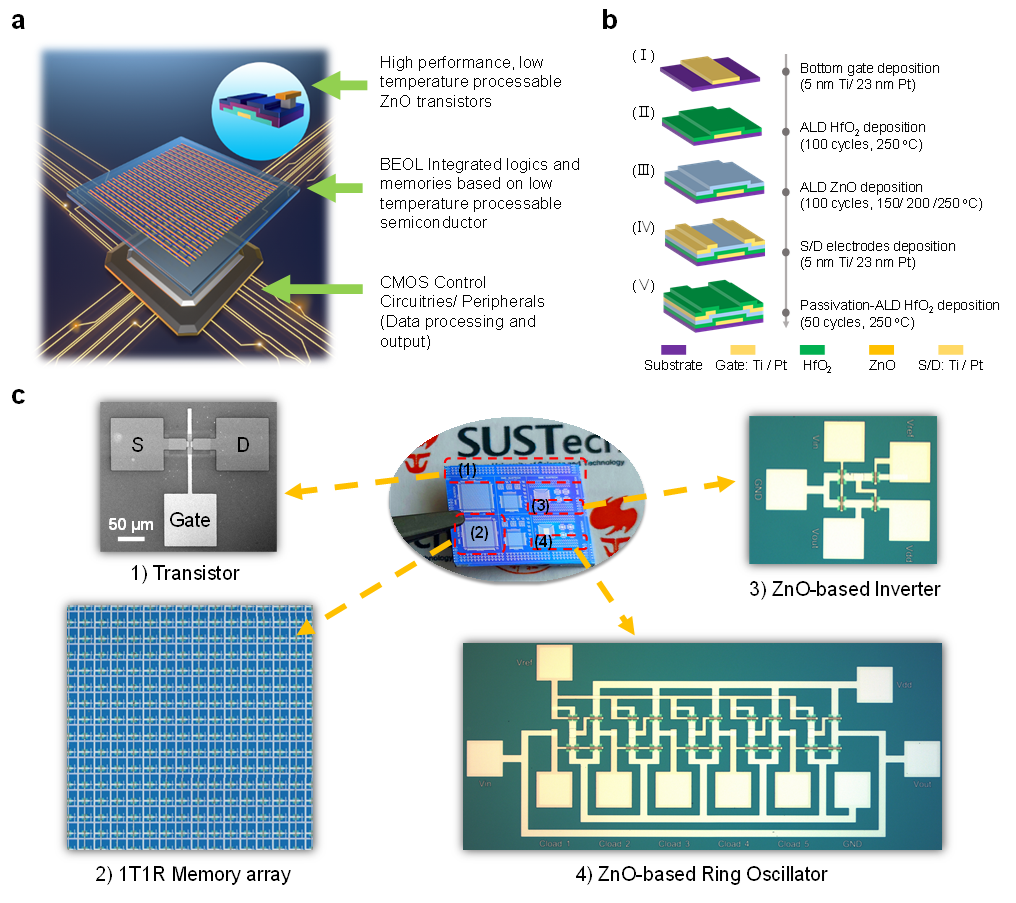

In response to the need of the microelectronics industry, Assistant Professor Yida Li’s group from the School of Microelectronics at the Southern University of Science and Technology (SUSTech), in collaboration with Assistant Professor Longyang Lin from the same department and Professor Panpan Zhang from Beijing University of Post and Telecommunications (BUPT), adopted a Design Technology Co-Optimization (DTCO) approach, encompassing materials, device, compact modelling, and circuit design to demonstrate the potentials of ZnO, a low-temperature processable oxide semiconductor implemented in BEOL memory arrays and circuitries.

Their work, entitled “CMOS backend-of-line compatible memory array and logic circuitries enabled by high performance atomic layer deposited ZnO thin-film transistor”, has been published in Nature Communications.

Yida Li’s research group spent one year rigorously fine-tuning the deposition process of ALD ZnO thin-film, eventually realizing record electron mobility (up to 140 cm2/V.s) among existing reported ALD ZnO thin-film. The exceptional performance of the device allows its implementation as a select transistor in a 1 kbit 1T1R memory array for memory-centric computing. Furthermore, using a DTCO approach for a NMOS-only circuit design, they experimentally demonstrated several inverter types and their corresponding ring oscillators with potentials to operate beyond 10’s of MHz. Using these initial results as a guide, the researchers are confident to push the limits of BEOL circuit performance even further, bringing such technology one step closer to future IC chips.

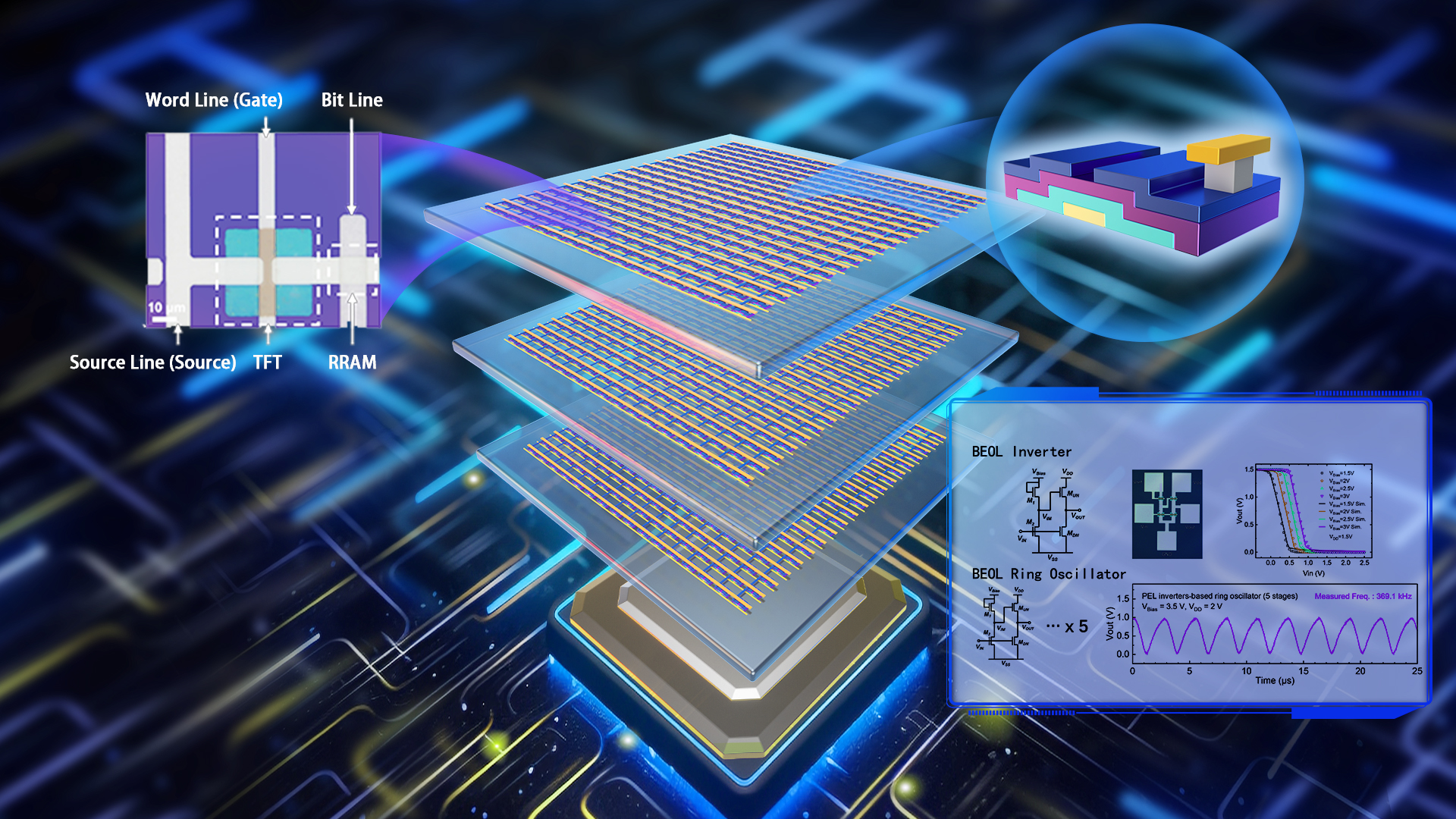

Figure 1. ZnO as CMOS-BEOL-compatible transistor material

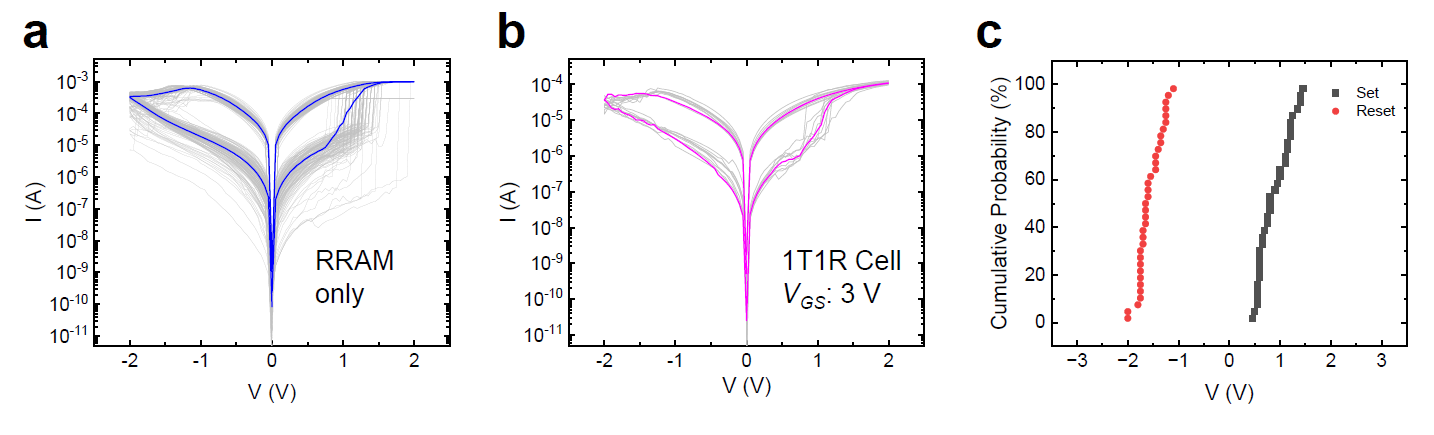

Figure 2. ZnO is used as select transistors in a 1 kbit 1T1R memory array

Figure 3. ZnO implemented in inverters

Figure 4. ZnO implemented in ring oscillators

Wenhui Wang, a Ph.D. student from Assistant Professor Yida Li’s research group at SUSTech, is the first author of this paper. Ke Li, a visiting student in the same group, is the co-first author. Assistant Professor Yida Li is the main corresponding author, and Assistant Professor Longyang Lin and Professor Panpan Zhang are the co-corresponding authors. Other collaborators include the University of Hong Kong and Shanghai Jiao Tong University.

This work was supported by the National Natural Science Foundation of China (NSFC), Shenzhen Fundamental Research Program, and the Guangdong Provincial Department of Education Innovation Team Program. Technical support for this research was provided by the Core Research Facilities at SUSTech.

Paper link: https://doi.org/10.1038/s41467-023-41868-5

To read all stories about SUSTech science, subscribe to the monthly SUSTech Newsletter.

Proofread ByAdrian Cremin, Yingying XIA

Photo By