The field of integrated circuits lies at the heart of modern technology, driving advancements in artificial intelligence (AI), machine learning, data centers, and high-speed computing. As demands for higher data rates, energy efficiency, and miniaturization increase, significant challenges arise, such as crosstalk interference, signal integrity issues, and power constraints. Addressing these challenges through innovative designs and techniques is critical to enabling next-generation applications, ensuring efficient data transmission, and maintaining system reliability.

The research group led by Professor Quan Pan from the School of Microelectronics at the Southern University of Science and Technology (SUSTech) has recently made significant progress in high-speed wired chip design. The team has published four related journal papers, three of which were published in the top-tier journal IEEE Journal of Solid-State Circuits (JSSC), while one was invited to be published in the top open-access journal IEEE Open Journal of the Solid-State Circuits Society (OJ-SSCS) in the field of integrated circuit design.

Tackling crosstalk challenges in SE-MIMO systems

The increasing demand for high bandwidth and low-power wired communication in AI, machine learning, and high-performance data centers has driven the need for higher I/O density within limited chip areas and faster per-pin data rates. While previous studies have demonstrated the feasibility of achieving higher throughput links using advanced modulation schemes, complex equalization techniques, and forward error correction (FEC) methods, these approaches introduce significant hardware overhead, high latency, and increased power consumption.

Single-ended multiple-input multiple-output (SE-MIMO) schemes provide a promising solution by utilizing two single-ended signals over a pair of differential channels to achieve high data rates. However, high-performance SE-MIMO transmission depends on crosstalk cancellation (XTC) techniques because severe crosstalk arises from the coupling of connectors, packaging, and routing in the channels. Such severe crosstalk degrades the signal integrity (SI) of the link.

Additionally, different applications involve different channel characteristics, which necessitate XTC techniques that are both adaptive and robust. Since the signal-to-noise ratio (SNR) is highly sensitive in single-ended systems, crosstalk cancellation methods must avoid excessive degradation of the SNR. Therefore, to mitigate strong crosstalk in tightly coupled differential channels and enable the deployment of SE-MIMO schemes across various scenarios, it is essential to develop an effective XTC method that is independent of channel characteristics.

To address the aforementioned issues, this paper proposes a single-ended transceiver with mode-encoded crosstalk cancellation. This approach effectively reduces interference and enables high-speed communication in tightly coupled channels. Through rigorous analysis, the researchers examined the mechanisms of crosstalk formation and the mathematical principles of their mode-encoded crosstalk cancellation method, comparing it with existing techniques.

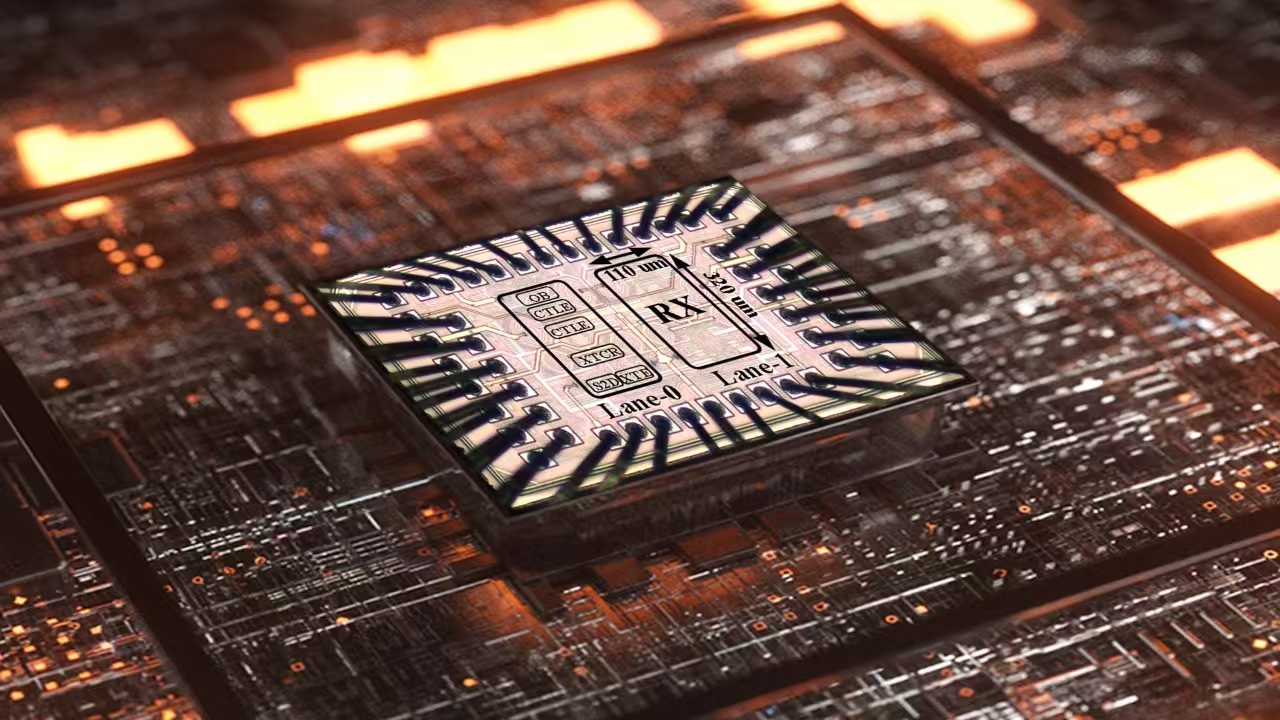

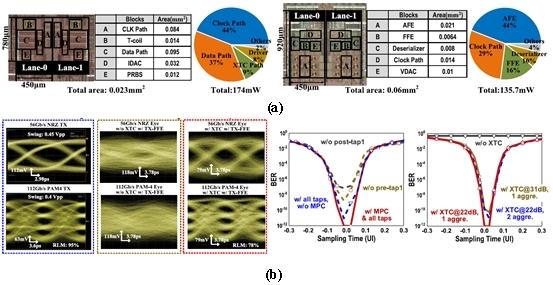

Figure 1. Mode coding crosstalk elimination transceiver chip

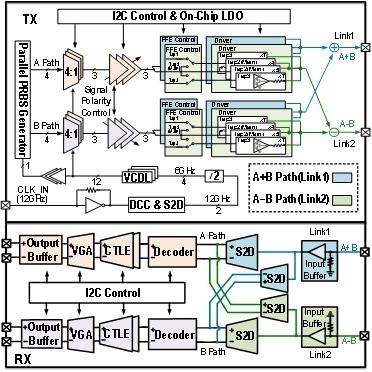

Figure 2. (a) Chip photograph; (b) Chip power consumption distribution; (c) Transceiver Eye Diagram; (d) Bit error rate test results

The proposed transceiver was verified in a practical two-channel system, achieving a data rate of 24 Gb/s per pin and maintaining a remarkably low bit error rate (BER) of 10⁻¹². Figure 2(a-b) illustrates the chip area and power consumption distribution of the transceiver, while Figure 2(c) presents the eye diagram test results under two-channel scenarios. Without crosstalk cancellation, the eye diagram of the transceiver completely closes after passing through the channel. When the crosstalk cancellation function is enabled, the eye diagram shows significant improvement, achieving an eye width of 0.34 UI (68 mV) and an eye height of 0.33 UI (32 mV) at 24 Gb/s Non-Return-to-Zero (NRZ). Furthermore, it highlights the system’s performance, showing the BER results under different conditions (Figure 2(d)).

This work, titled “A 2 × 24 Gb/s Single-Ended Transceiver With Channel-Independent Encoder-Based Crosstalk Cancellation in 28-nm CMOS”, has been published in JSSC.

Ph.D. student Hong-Zhi Wu is the first author of this paper, with Professor Quan Pan serving as the corresponding author. The School of Microelectronics at SUSTech is the first affiliated institution.

High-speed single-ended TRX for backplane links

With the rapid expansion of network switching and cloud computing, the demand for faster and more efficient wired transceivers (TRX) has soared, with data rates now reaching up to 224 Gb/s. While four-level pulse amplitude modulation (PAM-4) TRX based on digital signal processors (DSP) have proven effective in achieving these speeds, their high power consumption makes them unsuitable for power-sensitive applications, especially in very short-reach (VSR) and medium-reach (MR) links. These systems also face packaging challenges as bandwidth requirements continue to increase.

Alternatively, adopting higher-level pulse amplitude modulation (PAM) schemes can relax the I/O bandwidth requirements. As shown in Figure 3, a 224 Gb/s PAM-4 scheme requires a bandwidth of 56 GHz, while PAM-8 and PAM-16 schemes reduce the bandwidth requirements to 37 GHz and 28 GHz, respectively.

Single-ended solutions offer a promising alternative by leveraging two single-ended signals over a pair of differential channels to achieve high data rates. Compared to differential approaches, this method doubles the throughput density and relaxes the Nyquist Bandwidth requirements of passive components. Unfortunately, single-ended solutions face significant challenges due to crosstalk noise, which arises from connectors and packaging in backplane links.

The researchers developed a 2×112 Gb/s single-ended crosstalk cancellation TRX, designed for backplane links with connectors, achieving a total data rate of 224 Gb/s over a pair of differential channels.

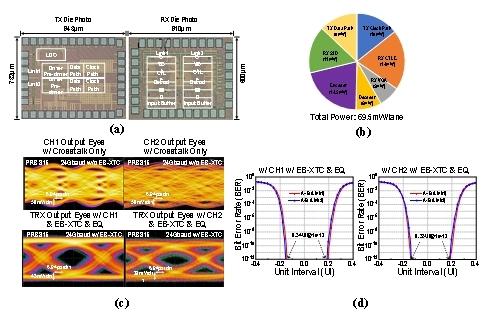

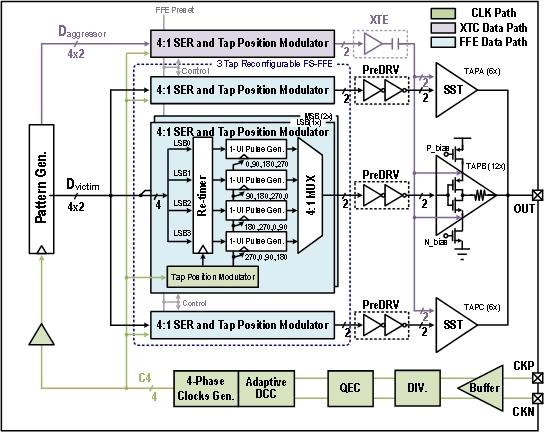

Figure 3. Single-ended multi-input multi-output crosstalk elimination receiver chip

Figure 4. (a) Chip photograph and power consumption distribution; (b) Chip eye diagram and bit error rate test results

The TRX’s performance was thoroughly validated through rigorous testing. Figure 4(a) highlights the chip’s area and power consumption distribution, while Figure 4(b) presents the test results of the eye diagram and bit error rate. Under conditions without crosstalk, the TRX achieved an eye width/height of 0.6 UI/224 mV for 56 Gb/s NRZ and 0.29 UI/45 mV for 112 Gb/s PAM-4. When crosstalk cancellation was enabled, the eye width showed significant improvement by an average of 0.42 UI for 56 Gb/s NRZ and 0.22 UI for 112 Gb/s PAM-4.

This study successfully achieved 112 Gb/s PAM-4 with a channel loss of 31 dB at 28 GHz and an energy efficiency of 2.77 pJ/b. Furthermore, the system maintained a BER of 10-10 for 112 Gb/s PAM-4, showcasing its reliability for high-speed communication.

This work, titled “A 2×112 Gb/s/pin Single-Ended Crosstalk Cancellation Transceiver With 31 dB Loss Compensation in 28-nm CMOS”, has been published in JSSC.

Ph.D. student Li-Ping Zhong is the first author of this paper, with Professor Quan Pan serving as the corresponding author. The School of Microelectronics at SUSTech is the first affiliated institution.

High-efficiency crosstalk cancellation for PAM-4 signaling

With the development of large-scale computing and AI applications, the demand for memory interface data throughput is constantly increasing. The two key indicators affecting memory interface throughput are the single-channel data rate and channel density. Due to the slowing down of bandwidth improvements from process scaling, advanced DRAM applications like GDDR6X have adopted PAM-4 signaling to increase data transfer rates. However, PAM-4 signaling, due to its reduced voltage margin, is more sensitive to SNR.

As the channel spacing decreases, crosstalk-related signal integrity issues become more severe, which significantly limits the improvement of channel density and data throughput. Although some transmitter crosstalk cancellation techniques have been reported, these techniques mainly focus on NRZ and suffer from either low SNR or low interface efficiency. Therefore, there is a need to explore a high-speed PAM-4 crosstalk cancellation technique that ensures both high SNR and high interface efficiency.

In this study, the researchers present a novel solution to these challenges: an integrated pre-emphasis capacitor-peak crosstalk cancellation technique. This innovative approach integrates a capacitor-peaking circuit within the transmitter driver, enabling the generation of a crosstalk cancellation signal. This signal maintains the output swing without increasing parasitic accumulation at the output node, ensuring efficient high-speed operation.

The proposed technology was implemented in a 4-channel high-speed PAM-4 crosstalk cancellation single-ended transmitter, achieving impressive results. Under channel conditions with -11 dB insertion loss and -15.8 dB crosstalk intensity, the transmitter demonstrated a maximum single-channel transmission rate of 64 Gb/s PAM-4, with an energy efficiency of just 1.27 pJ/bit.

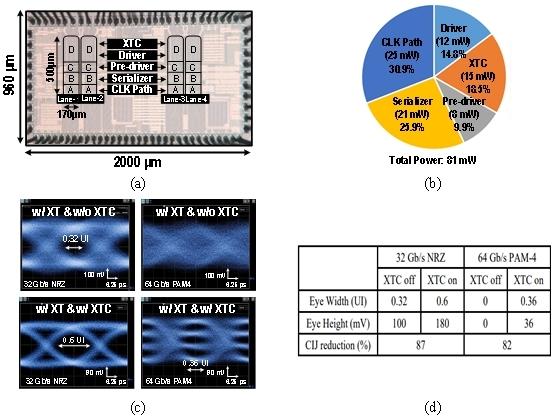

Figure 5. Capacitor peaking crosstalk cancellation high-speed single-ended PAM-4 transmitter chip

Figure 6. (a) Chip photograph; (b) Chip power consumption distribution; (c) Transmitter eye diagram; (d) Crosstalk jitter cancellation test results

Performance testing showcased the effectiveness of the crosstalk cancellation technique. Figures 6(a) and (b) show the chip area and power consumption distribution, while Figure 6(c) presents the eye diagram test results before and after enabling the crosstalk cancellation function. When the crosstalk cancellation function is disabled, the eye diagram for 32 Gb/s NRZ showed an eye width of 0.32 UI and a height of 100 mV, and the 64 Gb/s PAM-4 diagram was completely closed.

After enabling the crosstalk cancellation function, the eye width and eye height improved to 0.6 UI (180 mV) and 0.36 UI (36 mV) for 32 Gb/s NRZ and 64 Gb/s PAM-4, respectively. Figure 6(d) further highlights the success of the technique, achieving a crosstalk-induced jitter cancellation rate of 87% for 32 Gb/s NRZ and 82% for 64 Gb/s PAM-4 modes.

This work, titled “A 64 Gb/s/pin Single-Ended PAM-4 Transmitter with a Merged Pre-Emphasis Capacitive-Peaking Crosstalk Cancellation Scheme for Memory Interfaces in 28-nm CMOS”, has been published in JSSC.

Ph.D. student Wei-Tao Wu is the first author of this paper, with Professor Quan Pan serving as the corresponding author. The School of Microelectronics at SUSTech is the first affiliated institution, with Pengcheng Laboratory as the second affiliated institution.

Design innovations for single-ended wireline crosstalk cancellation

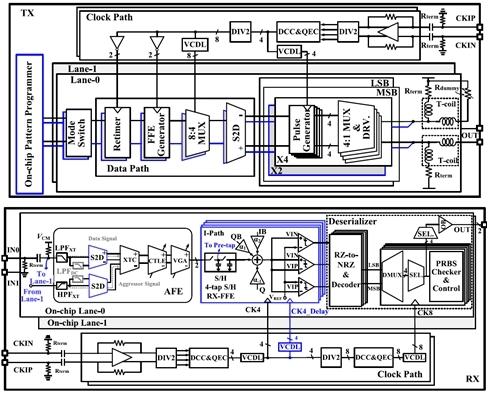

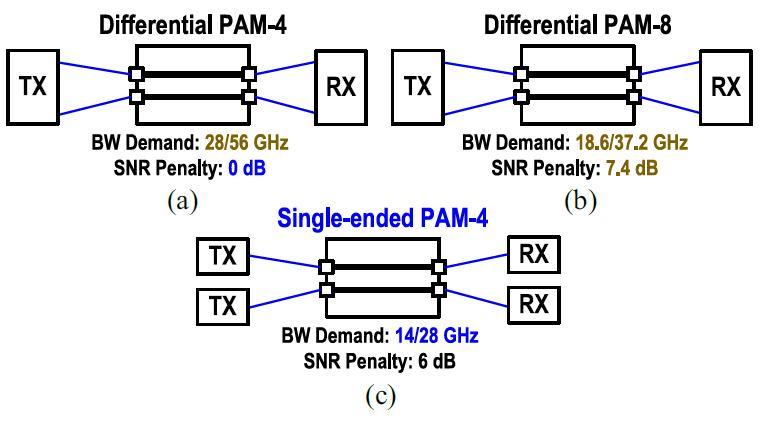

In AI applications, data centers need to support increasingly higher data rates to manage massive datasets. Several potential solutions have been proposed to achieve data rates of up to 224 Gb/s per channel. One of the main approaches is the use of PAM-4 TRX in advanced technologies, which can achieve the required target data rate of 224 Gb/s (Figure 7). However, due to the increased bandwidth demand and significant equalization requirements, this solution faces severe challenges from link loss and high power consumption.

An alternative approach involves using higher-order PAM schemes, such as PAM-8. These schemes encode more data per symbol and require less channel bandwidth compared to PAM-4. However, they suffer from a significant SNR loss of about 7.4 dB and are more susceptible to defects such as jitter and reflections.

Another promising option is the single-ended PAM-4 scheme, which doubles the data throughput by utilizing two single-ended signals across a differential pair of channels. This approach reduces the bandwidth requirement to half that of differential PAM-4 or the same data rate (Figure 7(c)). However, it faces significant challenges, particularly from far-end crosstalk (FEXT), due to its halved signal swing, resulting in an SNR loss of about 6 dB.

Figure 7. (a) Differential PAM-4 scheme; (b) Differential PAM-8 scheme; (c) Single-ended PAM-4 method comparison

This paper provides a comprehensive analysis of single-ended schemes and compares it with the differential PAM-4 and PAM-8 schemes. It also reviews basic crosstalk cancellation techniques and proposes innovations that enable a single-ended crosstalk cancellation receiver to achieve high data rates. The researchers introduce advanced design techniques for a receiver capable of supporting data rates of up to 56 Gb/s and 112 Gb/s per channel using PAM-4 signaling in 28nm CMOS technology. These receivers achieve bit error rates of <10^-10 and <10^-12, respectively, with single-ended channel losses of 24 dB and 25 dB.

This work, titled “Design Techniques for Single-Ended Wireline Crosstalk Cancellation Receiver Up to 112 Gb/s”, has been published in OJ-SSCS. The paper was invited for publication in the Special Issue on High-Performance Wireline Transceiver Circuits.

Li-Ping Zhong is the first author of this paper, with Professor Quan Pan serving as the corresponding author. The School of Microelectronics at SUSTech is the first affiliated institution.

Paper links (In order of appearance above):

JSSC: https://ieeexplore.ieee.org/document/10777044

JSSC: https://ieeexplore.ieee.org/document/10770123

JSSC: https://ieeexplore.ieee.org/document/10781378

OJ-SSCS: https://ieeexplore.ieee.org/document/10757331

To read all stories about SUSTech science, subscribe to the monthly SUSTech Newsletter.

Proofread ByAdrian Cremin, Yingying XIA

Photo BySchool of Microelectronics