The 2025 IEEE International Solid-State Circuits Conference (ISSCC 2025) recently took place in San Francisco, USA, where two papers from Professor Quan PAN’s team of the School of Microelectronics at the Southern University of Science and Technology (SUSTech) were selected for presentation.

The conference venue

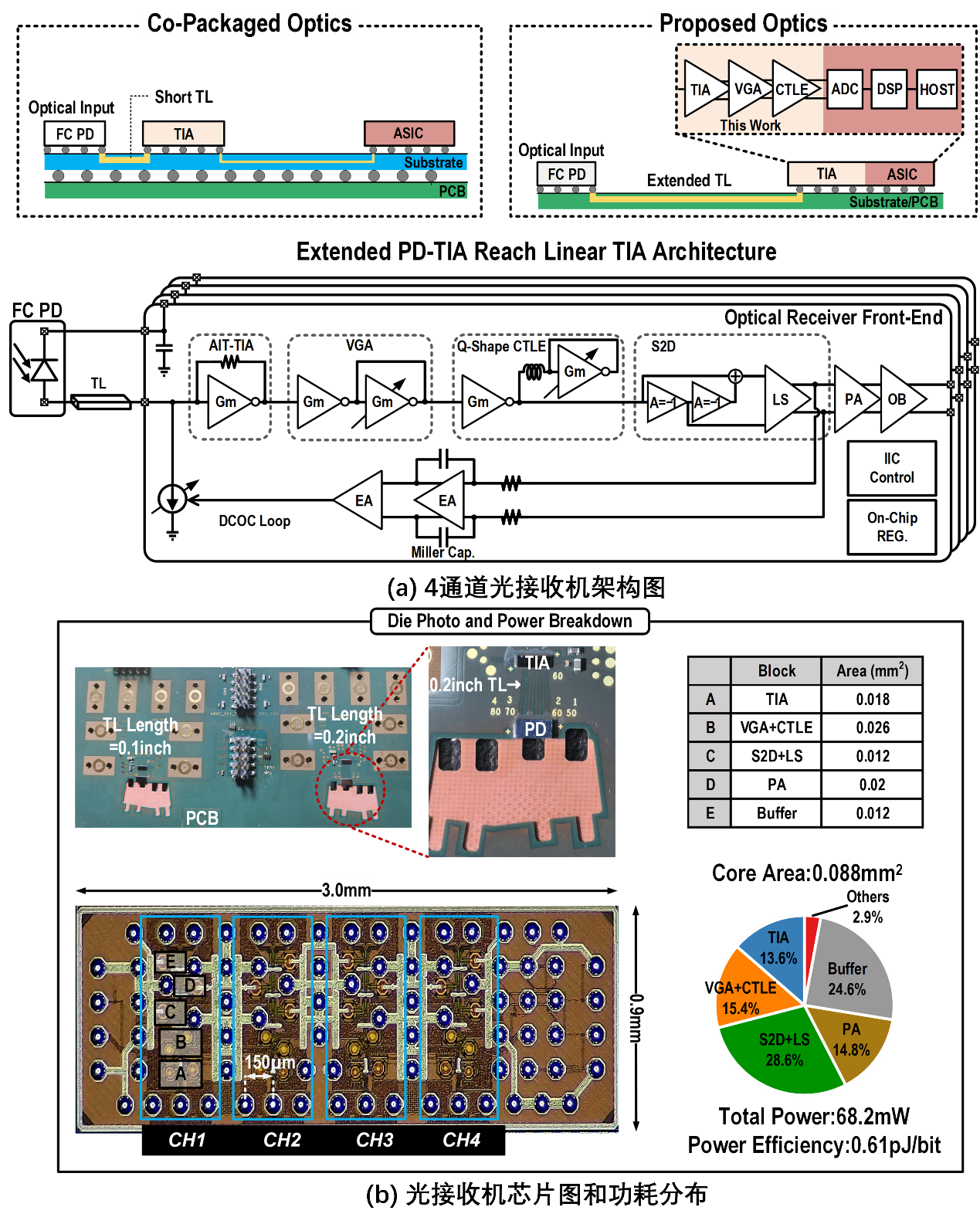

Paper 1: A 112Gb/s 0.61pJ/b PAM-4 Linear TIA Supporting Extended PD-TIA Reach in 28nm CMOS

The growing demand for cloud storage and artificial intelligence applications is driving optical communication technologies to evolve toward higher data rates and lower costs. Co-packaging the photodetectors (PDs), BiCMOS transimpedance amplifiers (TIAs), and CMOS switch application-specific integrated circuits (ASICs) within the same package can significantly enhance signal integrity, reduce power consumption, and increase integration density, all while lowering costs. Additionally, integrating TIAs into switch ASICs using CMOS processes further reduces the overall component count, leading to even lower costs and power consumption.

To ensure thermal expansion adaptability of the ASIC, optical coupling flexibility, and mechanical stability, while avoiding field replacement issues caused by excessively short PD-TIA distances, careful design of the PD-TIA reach is necessary to optimize interconnection bandwidth density of the optoelectronic interface. However, increasing the PD-TIA reach can result in stronger signal reflections, degraded in-band amplitude flatness, and reduced bandwidth.

Addressing these challenges from both system architecture and circuit design perspectives, the research team developed a 4×112Gb/s PAM-4 TIA based on an active input termination transimpedance amplifier (AIT-TIA), a Q-shape continuous-time linear equalizer (CTLE), and a signal-interpolated single-ended-to-differential converter (S2D). This design achieves an energy efficiency of 0.61 pJ/b and supports a PD-TIA reach of 0.2 inch, marking the longest PD-TIA reach among all types of optical receivers currently available domestically and internationally.

Yangyi ZHANG, a master’s student at SUSTech, is the first author of this paper, with Professor Quan PAN serving as the corresponding author.

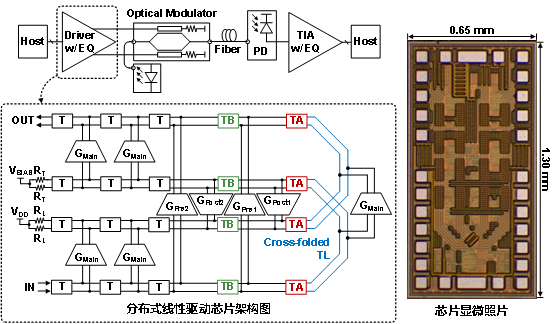

Paper 2: A 100Gbaud 4Vppd Distributed Linear Driver with Cross-folded Transmission Lines and Cross-coupled Gm Cells for Built-in 5-tap FFE in 130nm SiGe BiCMOS

The research team developed a linear driver chip for optical modulators designed for linear direct-drive pluggable optical links. They introduced a distributed topology that incorporates cross-coupled active units and cross-folded transmission lines. This design leverages the parasitic inductance of the transmission line to counteract the parasitic capacitance from the large-swing active transconductance units, enabling higher bandwidth. Additionally, the driver chip features five amplification paths with varying delays between the input and output ports, effectively creating a 5-tap built-in feedforward equalizer to improve the chip’s equalization performance.

Fuzhan CHEN, a joint Ph.D. student of SUSTech and the Hong Kong University of Science and Technology (HKUST), is the first author of this paper. The co-corresponding authors are Professor Quan PAN and Professor C. Patrick Yue from HKUST, with SUSTech serving as the primary institution for this work.

These two studies were supported by the National Key R&D Program and the National Natural Science Foundation of China (NSFC).

Students from Quan PAN’s team at ISSCC

The ISSCC, organized by the IEEE Solid-State Circuits Society (SSCS), is widely regarded as the premier conference in the field of integrated circuit design, often referred to as the “Olympics of Integrated Circuit Design”. Founded in 1953, ISSCC is traditionally the venue where the most cutting-edge solid-state circuit technologies are first presented. Each year, it attracts over 3,000 participants from academia and industry worldwide. To date, SUSTech has published eight papers at ISSCC as the primary institution, five of which were authored by Professor Quan PAN’s team.

At this year’s conference, two Ph.D. students from the team, Liping ZHONG and Fuzhan CHEN, were honored with the 2024-2025 Pre-Doctoral Achievement Award by SSCS. This award recognizes outstanding doctoral students in the field of integrated circuit design globally. This is the first time that students from SUSTech have received this honor. Both students, who are among the first to graduate from the team’s doctoral program, have gone on to secure academic positions at universities.

Liping ZHONG and Fuzhan CHEN award certificates

These achievements reflect SUSTech’s growing international competitiveness in the field of solid-state circuit research. In the future, the School of Microelectronics at SUSTech will continue to devote itself to cultivating more research talents with a global perspective and academic potential, contributing to the advancement of discipline development and technological innovation.

Related paper links (In order of appearance above):

Proofread ByAdrian Cremin, Yuwen ZENG

Photo BySchool of Microelectronics