近日,南方科技大学深港微电子学院李毅达助理教授课题组在CMOS后道集成和氧化物半导体领域取得重要进展。相关成果以“CMOS Backend-of-Line Compatible Memory Array and Logic Circuitries Enabled by High Performance Atomic Layer Deposited ZnO Thin-film Transistor”为题发表在国际顶级期刊 Nature Communications 上。

随着对数据驱动型应用(例如新一代机器学习加速器和物联网)需求的持续增长,传统的冯诺依曼架构面临着严重的“存储墙”挑战,硅基晶体管工艺制程的缩小进一步加剧了这种情况。为了突破该瓶颈,集存储单元和计算单元为一体的单片三维集成或者存内计算,成为一种潜在的解决方案。但用于CMOS后端集成的硅基技术受到低热负载(< 400 ℃)的限制,二维材料、氧化物半导体等这些超硅器件可以很好地兼容CMOS后端工艺。

氧化物半导体具有工艺温度低、透明度好、薄膜可大面积生长、电子迁移率高、能带隙宽等优点,这些优点使其适用于内存驱动电路以及基于高性能薄膜晶体管的逻辑电路。随着人们对实现具有新功能和超强计算能力的新型计算架构越来越感兴趣,开发高性能氧化物半导体晶体管以实现兼容CMOS 后端工艺的单片三维集成(M3D)电路已迫在眉睫。

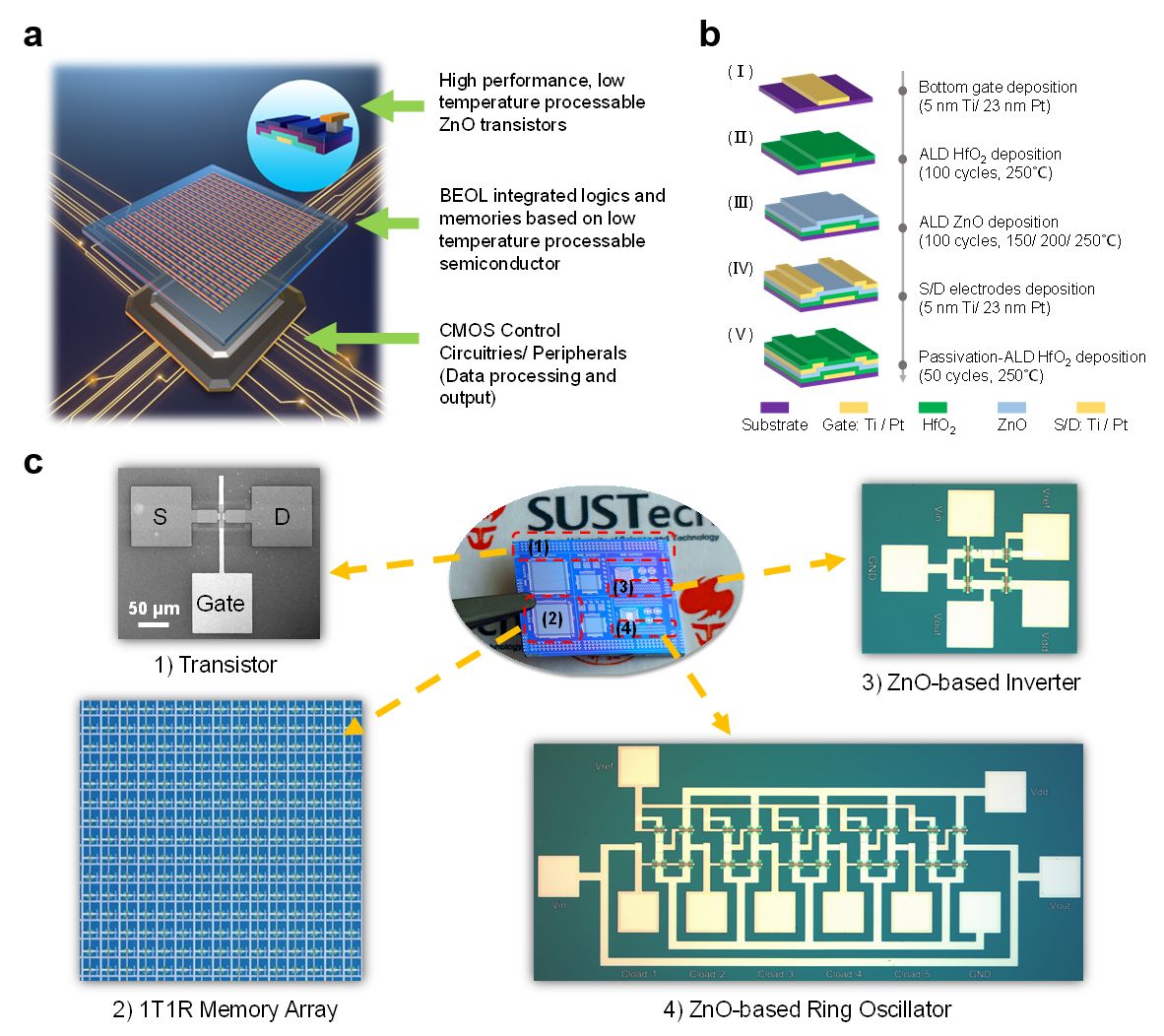

图:可兼容CMOS后端集成的ZnO薄膜晶体管,及其存储阵列和逻辑电路

在这项工作中,首先利用原子层沉积(ALD)工艺,实现了基于多晶ZnO半导体的高性能薄膜晶体管(TFT),该TFT的电子迁移率可达140 cm2/V·s,电流开关比>108,栅极漏电流<10-11 A。随后将该TFT集成到忆阻器(RRAM)阵列中,实现了可高速读取的1 kBit(32×32)的1T1R存储阵列。为了协同设计基于TFT的电路,该工作还对ZnO TFT做了器件建模(Compact Model),基于该器件模型,并实现了一个基于纯NMOS设计反相器的5级环形振荡器,该环形振荡器的工作频率可以达到44.85 MHz。

李毅达课题组2022级博士研究生王文辉为论文第一作者,李毅达为第一通讯作者,北京邮电大学特聘研究员张盼盼和南方科技大学深港微电子学院助理教授林龙扬为共同通讯作者,南科大为论文第一单位。该工作得到了深港微电子学院以及其他合作单位(北京邮电大学、香港大学、上海交通大学)老师的支持。该论文研究工作得到国家自然科学基金面上项目和省级、市级科研经费的支持。

论文链接:https://www.nature.com/articles/s41467-023-41868-5

供稿:深港微电子学院

通讯员:杜玉梅

主图:丘妍

编辑:朱增光