The research team led by Professor Junmin JIANG from the Department of Electronic and Electrical Engineering at Southern University of Science and Technology (SUSTech) has made significant progress in analog circuit sizing optimization. The related work, titled “FD-MAGRPO: Functionality-Driven Multi-Agent Group Relative Policy Optimization for Analog-LDO Sizing,” has been accepted by AAAI-26, a premier international conference on artificial intelligence.

Figure 1: Traditional analog circuit sizing requires expert experience, while reinforcement learning can accelerate the sizing process

Circuit sizing is a critical phase in analog integrated circuit design requiring the determination of specific parameter values for each transistor’s width, length, and finger count, as well as resistor and capacitor values, to meet multiple performance specifications, including gain, power consumption, and stability. Unlike highly automated digital circuit design, analog circuit sizing heavily relies on engineer expertise. In practice, a low-dropout regulator (LDO) circuit often contains dozens to hundreds of design parameters. Engineers must repeatedly adjust parameters and run simulations for verification—a process that takes weeks or even months, severely limiting chip development efficiency.

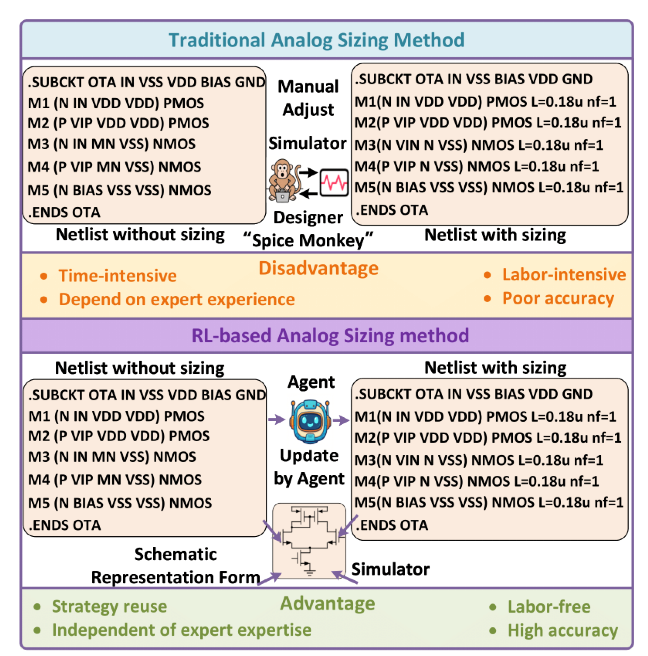

Figure 2: FD-MAGRPO Algorithm Flow

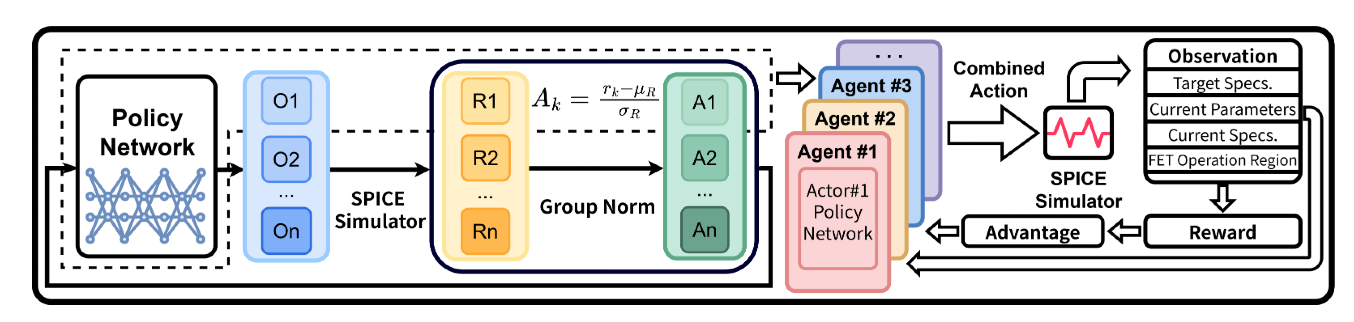

Figure 3: LDO circuit topologies used in experiments and the proposed function-based grouping method

The SUSTech team proposed the FD-MAGRPO algorithm to address this challenge. The algorithm achieves two key technical innovations: First, it employs a critic-free network architecture that eliminates training instability caused by value estimation bias in traditional actor-critic reinforcement learning methods, making the algorithm more efficient and achieving faster convergence. Second, it introduces a functionality-driven grouping strategy that optimizes circuit components based on their functional roles rather than physical locations. This grouping approach allows components with similar behaviors to be controlled by the same agent, significantly improving coordination efficiency among multiple agents.

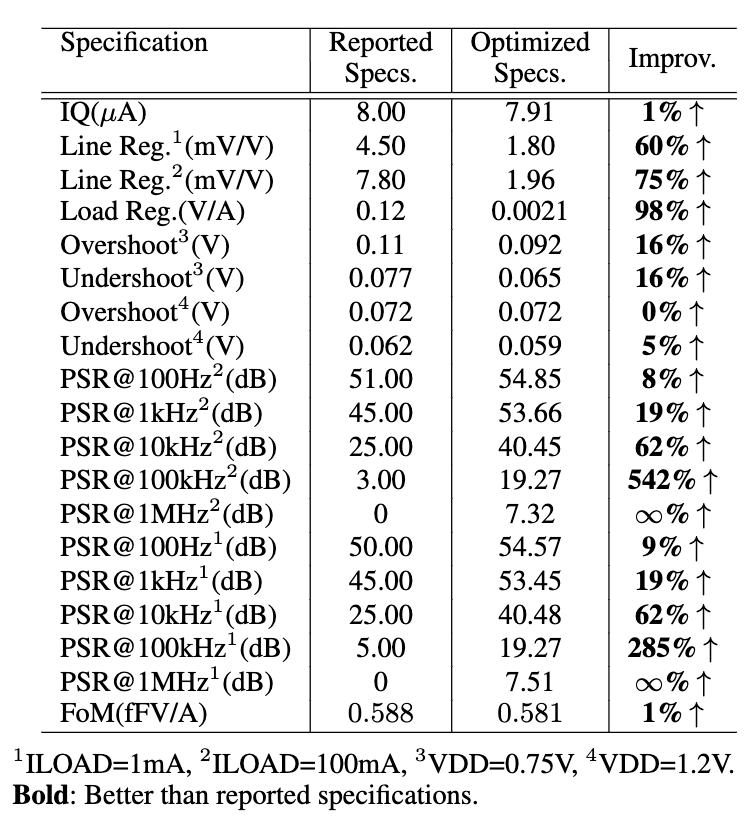

Figure 4: Optimization Results for LDO#3 Circuit

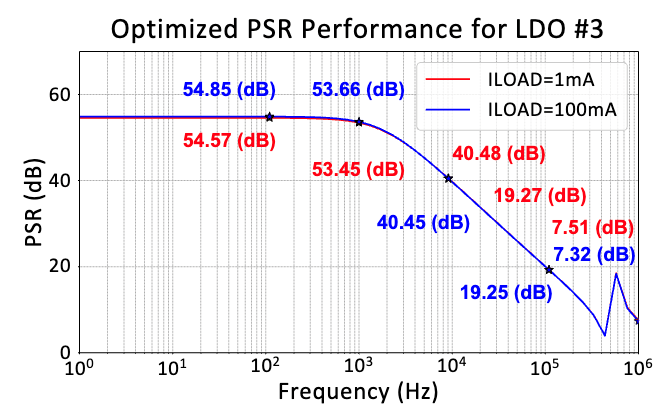

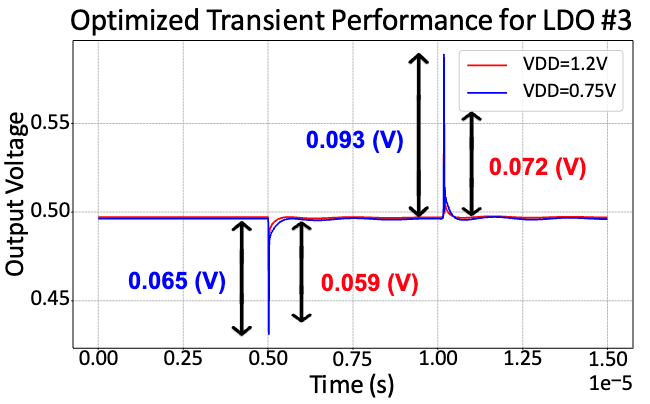

Figure 5: PSR and Transient Simulation Results for LDO#3 Circuit

On practical low-dropout regulator circuits containing 65-179 design parameters, this method completes sizing optimization with only 800-3000 simulations, achieving 4.8× to 13.0× speedup compared to existing methods. For the most complex test circuit, the optimized line regulation, load regulation, power supply rejection ratio, and other performance metrics improved by 16%-542% compared to the original reported values. This algorithm provides a new solution for complex analog circuit sizing optimization and promises to accelerate chip design workflows while reducing dependence on manual expertise.

Haoning JIANG, a senior undergraduate student from the Department of Electronic and Electrical Engineering, is the first author of the paper. Han WU, a PhD student from the SUSTech-University of Macau joint program, is the co-first author. SUSTech is the first affiliation, and Professor Junmin JIANG is the sole corresponding author. Notably, co-authors Zhuoli OUYANG and Ziheng WANG are also SUSTech undergraduate students, demonstrating the effectiveness of SUSTech’s undergraduate research training program.

Proofread ByNoah Crockett, Junxi KE

Photo ByHaoning JIANG